Prying Eyes: Schauer TB10012 battery charger Pg 24

lssue **2**/201<sup>-</sup> <u>www.edn</u>.com Changing times, steady goals Pg 9

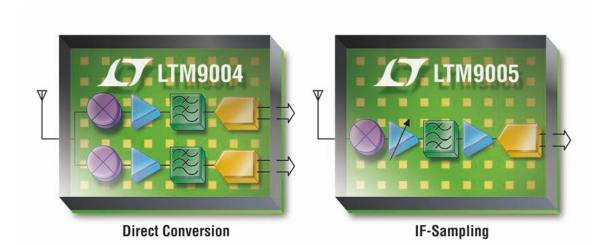

> Remote photo sensing Pg 22

Design Ideas Pg 47

Go ahead. Make my day! Pg 54

## BATTERY-STACK-MONITOR ICS SCRUTINIZE

HE CELLS

Page 36

**VOICE OF THE ENGINEER**

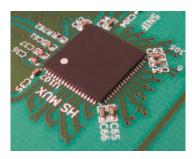

HARDWARE-BASED VIRTUALIZATION EASES DESIGN WITH MULTICORE PROCESSORS

Page 28

MANAGING SIGNAL INTEGRITY IN TOMORROW'S HIGH-SPEED FLASH-MEMORY-SYSTEM DESIGNS Page 44

#### Over 515,000 Products in Stock More Than 45,000 NEW Products Added in the Last 90 Days 440+ Suppliers

The industry's broadest product selection available for immediate delivery

#### www.digikey.com 1.800.344.4539

Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2011 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

# We're giving power a digital upgrade.

01011101100011

## Find out how our new Digital EXL Core<sup>™</sup> technology is redefining Power Factor Correction ICs.

Cirrus Logic's CS1500 and CS1600 are the industry's first Digital Power Factor Correction (PFC) ICs to surpass ordinary analog solutions in performance and price. Enabled by Cirrus Logic's EXL Core technology, these digital solutions intelligently solve traditional power management challenges with newly patented and patent pending designs that dramatically reduce the need for bulky, high-priced components and complex circuitry, lowering overall system cost and simplifying designs. Cirrus Logic now makes it possible for more energy-efficient power supplies in digital televisions, notebook adapters, PC power supplies and lighting ballast applications through advanced digital technology that creates smarter, greener, and more energyefficient products.

Experience Digital PFC. Register for free samples at www.cirrus.com/ednpfc

© 2010 Cirrus Logic, Inc. All rights reserved. Cirrus Logic, Cirrus, the Cirrus Logic logo designs, EXL Core, and the EXL Core logo design are trademarks of Cirrus Logic, Inc. EDN06242010

## Pick the best coupled inductor for your SEPIC converter in less time than it takes to read this ad.

(and have free samples on your desk tomorrow)

With over 135 coupled inductors to pick from, choosing the right one might seem difficult.

But our new on-line tools make it incredibly accurate and easy.

Enter data about your SEPIC converter and you'll get detailed specifications on all the

coupled inductors that meet your needs. A few more clicks gives you a detailed analysis of core and winding losses. The whole process can literally take less than a minute.

When you're done, be sure to ask for free evaluation samples. We'll ship them that same day.

Start your coupled inductor search at **coilcraft.com/sepic**

### Battery-stack-monitor ICs scrutinize the cells

Belectric-vehicle and data-center batteries need precise measurements using robust chips. by Paul Rako, Technical Editor

## EDN 1.20,11 contents

#### Hardware-based virtualization eases design with multicore processors

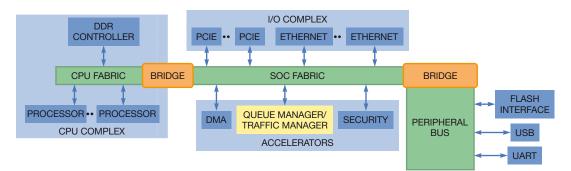

28 Offloading queue and traffic management to hardware reduces design complexity, improves application efficiency, and maximizes performance.

by Satish Sathe, AppliedMicro

- 12 Development kit tackles multi-dc/dc control strings for white and RGB LEDs

- 14 Ambarella augments image-processing foundation with increasing integration

- 14 Chinese company increases OLED lifetime

- 16 EDA tool accelerates place and route for SOCs

- 16 400-Gbyte MLC solid-state drives target enterprises

- 18 Microcontrollers operate as fast as 120 MHz

- 18 Gartner predicts Indian PC shipments to grow 25% in 2011

- 20 Voices: Samsung Electro-Mechanics' Jong-Woo Park: targeting smart-grid, electric-vehicle, and biotechnology applications

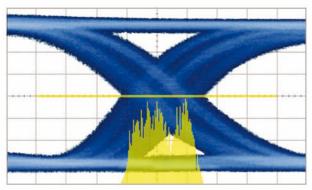

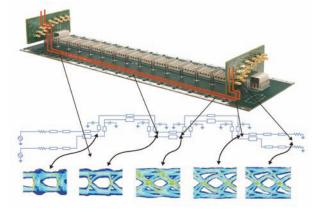

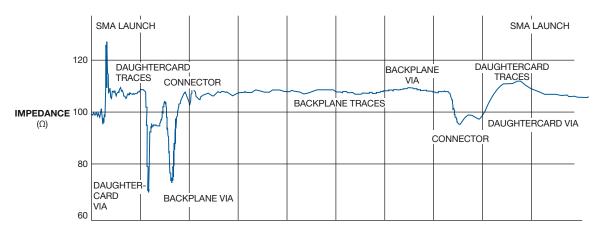

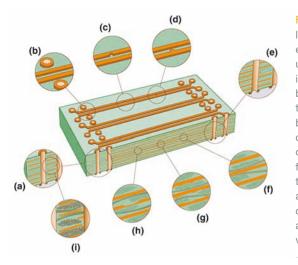

#### Managing signal integrity in tomorrow's high-speed flash-memory-system designs

44 Next-generation flashmemory technology will tout data-transfer rates as much as 10 times faster than currently available. However, increasing distortions in the data-carrying digital signals can cause datatransfer failures, complicating the management of signal integrity. Proper design strategies can help you deliver reliable, highperformance products.

> by Perry Keller, Agilent Technologies

COVER: DASHBOARD & LANDSCAPE: NARVIKK/ISTOCKPHOTO.COM; BATTERY ICON: VADYM TYNENKO/ISTOCKPHOTO.COM

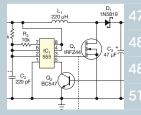

## DESIGNIDEAS

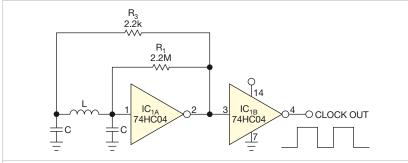

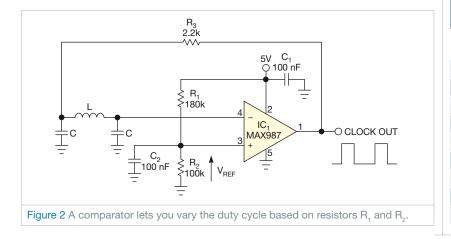

- Oscillator has voltage-controlled duty cycle

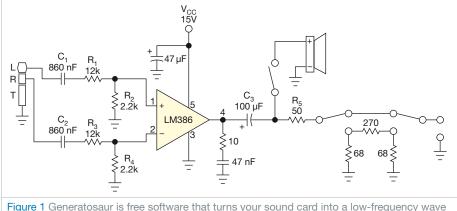

- Generate noisy sine waves with a sound card

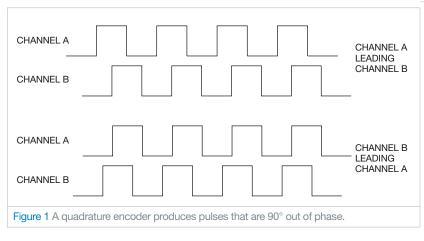

- Decode a quadrature encoder in software

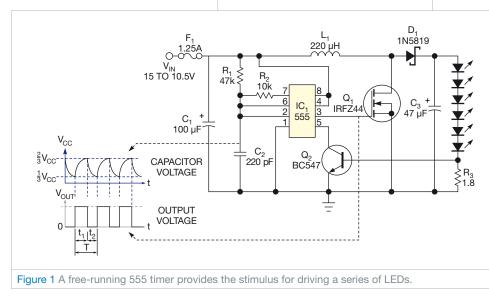

- Power an LED driver using off-the-shelf components

**MOUSER.COM** Semiconductors and electronic components for design engineers.

## We've got what design engineers need. **The future.**

You'll find the newest products for your newest designs. Get what's next at Mouser.

ser and Mouser Electronics are registered trademarks of Mouser Electronics. Inc. The Newest Products for Your Newest Designs is a registered trademark of Mouser Electronics. Inc.

### contents 12011

#### **DEPARTMENTS & COLUMNS**

- 9 EDN.comment: Changing times, steady goals

- 22 Baker's Best: Remote photo sensing

- 24 Prying Eyes: The Schauer TB10012 battery charger

- 26 Mechatronics in Design: You can't just say it's reliable

- 52 Product Roundup: Optoelectronics/Displays, Discrete Semiconductors

- 54 Tales from the Cube: Go ahead. Make my day!

#### **EDN** online contents

www.edn.com

#### ONLINE ONLY

Check out these Web-exclusive articles:

#### Critical false-path analysis through sensitization methods

Static and dynamic false-path determination is essential for accurate application of false paths in an SOC design. >www.edn.com/110120toca

#### Ensuring form, fit, and function for advanced interactive digital displays

The environment in which end-user equipment will be deployed has a critical influence on hardware selection, including the display front panel, which must provide a carefully optimized blend of optical, mechanical, and electrical properties.

→www.edn.com/110120tocb

#### **READERS' CHOICE 2010**

Take a look at 20 of the most-clicked-on articles and blog posts from across EDN.com in 2010.

→www.edn.com/110120tocc

#### PRYING EYES

In EDN's Prying Eyes, we peer inside an enduser consumer gadget, a reference design, or any other interesting electronicsenabled thing we can get a good look at. Unlike your average bill-ofmaterials tear-down, Prying Eyes aims to illuminate the tough decisions the engineers responsible for the design had to make. www.edn.com/pryingeyes

#### What's happening in the electronics world?

The EDN.com News Center provides real-time breaking news and analysis on the global electronics industry, including coverage of semiconductors, lawsuits, IC design, microprocessor units, consumer electronics, analog, and business trends. www.edn.com/110120tocd

EDN® (ISSN#0012-7515) is published semimonthly, 24 times per year, by UBM Electronics, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549; 310/445-4200; FAX 310/445-4299. Periodicals postage paid at Los Angeles, CA, and at additional mailing offices. SUBSCRIPTIONS-Free to qualified subscribers as defined on the subscription card, Rates for nonqualified subscriptions, including all issues; US, \$150 one year; \$250 two years; \$300 three years. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. For telephone inquiries regarding subscriptions, call 763/746-2792. E-mail: EDN@kmpsgroup.com. CHANGE OF ADDRESS—Notices should be sent promptly to PO Box 47461, Plymouth, MN 55447. Please provide old mailing label as well as new address. Allow two months for change. NOTICE—Every precaution is taken to ensure accuracy of content; however, the publisher cannot accept responsibility for the cor-rectness of the information supplied or advertised or for any opinion expressed herein. POSTMASTER—Send address changes to EDN, PO Box 47461, Plymouth, MN 55447. Canada Post: Publications Mail Agreement 40612608. Return undeliverable Canadian addresses to Pitney Bowes Inc, PO Box 25542, London, ON N6C 6B2. Copyright 2011 by United Business Media. All rights reserved. Reproduction in whole or part without written permission is prohibited. Volume 56, Number 2 (Printed in USA)

## Benchmark **MOSFETs**

Same Package, **60% More Current**

#### Logic Level

| Part<br>Number | B <sub>vdss</sub><br>(V) | R <sub>DS(on)</sub><br>4.5Vgs<br>(mΩ) | Q <sub>G</sub><br>4.5Vgs<br>(nc) | I <sub>D</sub> @<br>25°C<br>(A) | Package |  |  |  |

|----------------|--------------------------|---------------------------------------|----------------------------------|---------------------------------|---------|--|--|--|

| IRLS3034-7PPBF | 40                       | 1.7                                   | 108                              | 240*                            | D2PAK-7 |  |  |  |

| IRLB3034PBF    | 40                       | 2.0                                   | 108                              | 195*                            | T0-220  |  |  |  |

| IRLS3034PBF    | 40                       | 2.0                                   | 108                              | 195*                            | D2PAK   |  |  |  |

| IRLS3036-7PPBF | 60                       | 2.2                                   | 91                               | 240*                            | D2PAK-7 |  |  |  |

| IRLB3036PBF    | 60                       | 2.8                                   | 91                               | 195*                            | T0-220  |  |  |  |

| IRLS3036PBF    | 60                       | 2.8                                   | 91                               | 195*                            | D2PAK   |  |  |  |

| IRLS4030-7PPBF | 100                      | 4.1                                   | 87                               | 190                             | D2PAK-7 |  |  |  |

| IRLB4030PBF    | 100                      | 4.5                                   | 87                               | 180                             | T0-220  |  |  |  |

| IRLS4030PBF    | 100                      | 4.5                                   | 87                               | 180                             | D2PAK   |  |  |  |

| * Package lim  | ited                     |                                       |                                  |                                 |         |  |  |  |

#### **Features**

- Suited for industrial battery, power supply, high power DC motors, and power tools

- Industrial grade and MSL1

- RoHS compliant Your FIRST CHOICE

for Performance For more information call 1.800.981.8699 or visit www.irf.com

THE POWER MANAGEMENT LEADER

Visit us at Booth 409

07-09 March 2011

### Is Crosstalk Degrading Your 10G Multi-Channel IC Design?

Testing with fixed delay aggressors can result in induced interference outside of the critical receiver sampling time window.

A CON

Slewed delay assures finding all crosstalk problems.

#### 20 x 4 data switch...Running at 10 Gb/s...

first silicon due in 3 weeks...only one metal layer mask spin planned. You must find all the problems. You have lined up the test technicians, the lab space, the thermal testing station...

## How are you testing crosstalk susceptibility? If you are only driving

**ISCEPTIDITTY**: If you are only driving aggressor signals on the adjacent pair of unselected ports, you are at risk of missing crosstalk induced bit errors. Yet driving all the inactive ports with single channel BERTs or pattern generators is prohibitively expensive and requires more than a rack full of equipment.

#### The Centellax PCB12500 parallel

channel BERT is a compact, affordable alternative. Select pattern generators or error detectors for any of the five remote heads. Drive the deselected ports with either a clock or PRBS aggressor signal.

The PCB12500's exclusive slewed phase delay independently sweeps each aggressor's transition over a full UI. This creates the "perfect storm" of timing conditions that assures you will find low probability crosstalk susceptibility – those events that testing with fixed delay aggressors will miss.

To find out more about affordable solutions for signal integrity testing visit **www.centellax.com**

With your first silicon arriving in three weeks you had better call now.

Affordability without compromise

See us at DesignCon 2011, Booth #121

#### BY RON WILSON, EDITORIAL DIRECTOR

#### Changing times, steady goals

ou may have heard, if you follow such things, that UBM (United Business Media) has purchased Canon Communications, the publisher of *EDN*. UBM publishes *EE Times* and *ESD* magazine, among others. This acquisition is part of continuing reorganization in business-tobusiness publishing in response to a whole range of shifts

worldwide. The acquisition set off all manner of rumors in the advertising and public-relations worlds: UBM would close *EDN*, would fold it into the *EE Times* and *Designline* Web sites, or would redesign it to become the industry's first engineer-to-engineer animated comic book.

Well, sorry; as usual, the truth is more prosaic.

To begin with, *EDN* isn't going away. It is still here, and UBM is still committed to both the magazine and its network of Web communities. UBM still believes that working designers deserve

technical articles by and for engineers, standing apart from the streams of news and vendor-produced marketing pieces that clamor for your attention. It will continue to be, as its tag line says, the voice of the engineer.

So, what will change? For one thing, I am back at *EDN* after a brief absence. Rick Nelson, after somehow simultaneously managing to guide two major in-

dustry journals through some difficult transitions, has returned to being editor-in-chief of just *Test & Measurement*

*World*—rather than both that magazine and *EDN*.

Internal changes have also occurred, although these changes will more slowly become evident. The editorial teams of EDN, Test & Measurement World, Design News, ESD/Embedded.com, EE Times Designlines, EELife, and EE Times now all report to a senior vice president for content—and an engineer— Karen Field. For those of you as concerned as we are that advertiser influence should not intrude into editorial decisions, this change is a powerful reassurance.

The new organization also involves more expertise. We will continue to honor the distinction between engineer-written content and content from technically skilled nonengineers. We now have more voices from more technical specializations to call upon, however. We believe you will soon be reading the benefits.

We intend to keep another important distinction, as well. EDN has always been about what we might call foundational technologies: analog design; transforming, distributing, and delivering power; digital design; the use of processors and FPGAs; and the process of creating ICs. The material we publish comprises either staff-written or solicited and staff-edited, nonpromotional contributed articles. Some of the Designlines have a more application-oriented flavor, focusing on how vendors are approaching design problems in specific application areas. Especially in the print magazine, however, EDN will continue to focus on engineers writing about the foundations.

That's it in the proverbial nutshell. We will continue to bring you the best engineering articles from the most authoritative sources, be they working engineers, analysts, or our own staff. And we invite your feedback: This is a closed-loop system, and we need that error signal.

Thank you for being our readers, and welcome to an exciting 2011.EDN

Contact me at ron.wilson@ubm.com.

## **ANSYS® 13.0**

#### Smart engineering **Simulation** is now even **Smarter**.

In today's world of smart electronics, signal integrity, power integrity and EMI analysis are mission critical. Engineers must deliver both reliable and innovative products in evershrinking development cycles. For this reason, ANSYS is pleased to introduce ANSYS 13.0, our latest release which includes tools such as HFSS<sup>™</sup>, Slwave<sup>™</sup> and Ansoft Designer<sup>®</sup>, allowing engineers to identify and correct potential design or performance problems before they reach the marketplace.

ANSYS 13.0 can help your design team achieve an even shorter total time to solution with several new and advanced features, including:

- Greater accuracy and solution fidelity for very large electromagnetic structures through the use of new solvers

- Higher productivity through automated 3D electromagnetic model creation, resulting in more time to design and innovate

- Increased computational efficiency, through the use of HPC, resulting in a dramatic speedup of wide-frequency band or parametric simulations

For speed, reliability and accuracy, more product development leaders worldwide trust ANSYS for simulation solutions to help create smarter products in less time.

#### ANSYS 13.0 Advanced Fidelity. Higher Productivity. Leading Performance.

For more information, visit www.ansys.com/electronics13 or call us at 1.866.267.9724

## EDN

COLUMNISTS

Howard Johnson, PhD, Signal Consulting

Bonnie Baker, Texas Instruments

Pallab Chatterjee, SiliconMap Kevin C Craig, PhD, Marquette University

LEAD ART DIRECTOR

Marco Aguilera

ASSOCIATE ART DIRECTOR

Tim Burns

PRODUCTION

Michael Ciardiello,

Director of Premedia Technologies

Jeff Tade,

Production Director

Brian Wu,

Publications Production Manager

Jeff Polman, Derric Treece,

Senior Production Artists

William Baughman, Lucia Corona

Ricardo Esparza,

Production Artists

EDN EUROPE

Graham Prophet,

Editor, Reed Publishing

gprophet@reedbusiness.fr

EDN ASIA

Wai-Chun Chen,

Group Publisher, Asia

waichun.chen@ubm.com

Kirtimaya Varma, Editor-in-Chief

kirti.varma@ubm.com

EDN CHINA

William Zhang,

Publisher and Editorial Director

william.zhang@ubm.com

Jeff Lu.

Executive Editor

jeff.lu@ubm.com

EDN JAPAN

Katsuya Watanabe,

Publisher

katsuva.watanabe@ubm.com

Ken Amemoto

Editor-in-Chief

#### ASSOCIATE PUBLISHER, EDN WORLDWIDE

Judy Hayes, 1-925-736-7617; judy.hayes@ubm.com

> EDITORIAL DIRECTOR Ron Wilson 1-415-947-6317; ron.wilson@ubm.com

MANAGING EDITOR Amy Norcross Contributed technical articles 1-781-869-7971; amy.norcross@ubm.com

MANAGING EDITOR—NEWS Suzanne Deffree Electronic Business, Distribution 1-631-266-3433; suzanne.deffree@ubm.com

SENIOR TECHNICAL EDITOR

Brian Dipert Consumer Electronics, Multimedia, PCs, Mass Storage 1-916-548-1225; brian.dipert@ubm.com

TECHNICAL EDITOR Margery Conner Power Sources, Components, Green Engineering 1-805-461-8242; margery.conner@ubm.com

TECHNICAL EDITOR Mike Demler EDA, IC Design and Application 1-408-384-8336; michael.demler@ubm.com

> TECHNICAL EDITOR Paul Rako Analog, RF, PCB Design 1-408-745-1994; paul.rako@ubm.com

DESIGN IDEAS EDITOR Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@ubm.com

SENIOR ASSOCIATE EDITOR Frances T Granville, 1-781-869-7969; frances.granville@ubm.com

ASSOCIATE EDITOR Jessica MacNeil, 1-781-869-7983; jessica.macneil@ubm.com

CONSULTING EDITOR Jim Williams, Staff Scientist, Linear Technology edn.editor@ubm.com

CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com Robert Cravotta robert.cravotta@embeddedinsights.com

UBM Electronics ken.amemoto@ubm.com

#### EXECUTIVE OFFICERS

Paul Miller, Chief Executive Officer Fred Gysi, Chief Financial Officer Mike Deering, Chief Technology Officer Stephen Corrick, Vice President/Executive Director Kevin O'Keefe, Senior Vice President, Events Division Roger Burg, Vice President, Cyenations Jason Brown, Vice President, E-media

EDN. 33 Hayden Avenue, Lexington, MA 02421. www.edn.com. Subscription inquiries: 1-763-746-2792; EDN@kmpsgroup.com. Address changes: Send notice promptly to PO Box 47461, Plymouth, MN 55447. Please provide an old mailing label as well as your new address. Allow two months for the change.

UBM Electronics, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549; 1-310-445-4200; fax: 1-310-445-4299.

## PICO HIGH VOLTAGE

Over 2500 Std. Models Surface Mount and Thru-Hole

#### **DC-DC Converters** 2V to 10,000 VDC Outputs

Low Profile / Isolated Up to 10,000 Volts Standard Regulated Models Available

Call Toll Free 800-431-1064 • FAX 914-738-8225 E Mail: info@picoelectronics.com

#### EDITED BY FRAN GRANVILLE

#### **INNOVATIONS & INNOVATORS**

## Development kit tackles multi-dc/dc control strings for white and RGB LEDs

s LED-lighting designs become more complex, combining multiple strings of white or RGB (red/green/blue) LEDs, their control and drive circuits must also become more powerful. Texas Instruments' newest LED-development kit shows how you can use the low-cost but powerful Piccolo microcontroller to perform multidc/dc control for white and color LEDs. The kit includes separate dc/dc power stages to control two RGB- and two white-LED strings or as many as eight white-LED strings. The kit's C2000 Piccolo microcontroller has the bandwidth and processing power to control all of the power stages, as well as other functions, such as color mixing, PWM (pulsewidth-modulation) dimming, thermal sensing and correction, ambient-lighting compensation, and LED-fault protection. TI's development kits use a control board that lets you swap in a new controller board and evaluate different microcontrollers as they become available. The kit also includes a detachable LED panel with white and RGB LEDs.

Other features include eight digitally controlled dc/dc power stages, allowing developers to adjust cur-

rent levels to control color and brightness of individual strings; two SEPIC (single-ended-primaryinductance-converter) stages that support white LEDs; and six boost power stages that support color mixing for RGB-LED strings by providing individual current control of the red, green, and blue color components. The Piccolo F28027 control card provides 60 MHz of 32-bit performance; eight PWM channels; and a 13-channel, 12-bit ADC to support robust and flexible LED designs.

The device's GUI (graphical user interface) simplifies evaluation by providing simplified control to adjust power-stage current levels for experimentation with brightness and color mixing. Software-configurable maximum current allows for simple field upgrades and offers flexibility to adjust power stages in software as opposed to time-intensive redesign of system hardware. The devices also feature onboard isolated XDS100 USB (Universal Serial Bus) JTAG (Joint Test Action Group) emulation, which simplifies debugging and programming and reduces system cost.

Free, easy-to-use ControlSuite software includes examples for closed-loop average current control of dc/dc power LED-driver stages and detailed lab documentation of software structure and performance. The kit sells for \$499.—by Margery Conner >Texas Instruments, www.ti.com.

#### **TALKBACK**

"While a leap of imagination is still required, reading a mind may not be that far off ... for good or for ill. Who protects us all from misuse? Big Brother? Obama? I think not!!!"

-Researcher "HG," in *EDN's* Talkback Section, at http://bit. ly/ekrbxz. Add your comments.

> TI's LED-development kit lets you use the low-cost but powerful Piccolo microcontroller to perform multi-dc/dc control for white and color LEDs.

## Move Your Automated Test Beyond the Box

#### PRODUCT PLATFORM PXI modular instrumentation NI LabVIEW graphical software NI TestStand software

NI PXIe-107

>> Learn how PXI can help you at ni.com/beyond

800 891 8841

## pulse

## Ambarella augments image-processing foundation with increasing integration

mbarella last month unveiled its latest-generation image-processing platform, iOne, which includes a dual-core ARM Cortex-A9 system-processing nexus. Ambarella reports that its customers are increasingly embedding full-blown operating-system builds-specifically, Google's Android, due to its open-source and no-licensingfee attributes-in their system designs. As such, iOne's CPU integration negates the need to provide separate IC-systemprocessor facilities.

Ambarella also equipped iOne with an Imagination Technologies (www.imgtec.com) PowerVR SGX540 graphics core, along with incremental and improved system-interface ports versus those in the previous-generation A5S and A7.

Notably, iOne for the first time embeds a SATA (serial-

advancedtechnologyattachment) transceiver along with a GbE (gigabit-Ethernet) MAC (mediaaccess controller), whose bandwidth potential will come in handy in high-definition networkedcamera applications. The product also includes a 32-bit DDR3 SDRAM interface, which com-

bines high bandwidth potential with low bus pin count and finer-grained aggregate memory requirements versus a 64-bit bus alternative.

Like its precursors, iOne includes an ARM11 core to coordinate the activities of the

The iOne imageprocessing platform delivers an A5S++-class hybrid-camera function.

proprietary-architecture stillimage and video-DSP subsystems. However, Ambarella built iOne on the same 45-nm process as its predecessors: the A5S, which it introduced at the 2010 CES (Consumer Electronics Show), and A7, which it rolled out in September. The company fabricated the initial A5, which it unveiled during the 2009 CES, on a 65-nm lithography. To avoid a reticle-busting die size with requisite cost and yield negative impacts, Ambarella outfitted iOne with a subset of the A7's DSP resources, albeit still labeling the device as delivering an "A5S++-class hybrid-camera function."

Ambarella's iOne is currently available for sampling to lead customers, with production capability slated for early in the second quarter of this year. It costs \$25 (volume quantities). For those of you hoping to catch the 3-D wave; the chip embeds dual imagesensor interfaces and therefore integrates the left-plus-righteye, dual-stream-combining function that the company's stand-alone S3D Full HD camera preprocessing previously handled. - by Brian Dipert Ambarella.

www.ambarella.com.

#### Chinese company increases OLED lifetime

LEDs (organic lightemitting diodes) have several advantages over traditional LEDs: OLEDs can be less expensive to manufacture; can serve as rugged, colorful displays for handheld

devices, monitors, and TVs; and can potentially serve as large-surface-illumination/lighting devices. Imagine wallpaper that also illuminates a room.

Despite those features, OLEDs have relatively short lifetimes.

For example, the Osram (www. osram.com) Orbeos OLED lasts for approximately 500 hours, compared with LED lifetimes of 20,000 hours and beyond.

Targeting this problem, Chinese OLED company Visionox and Tsinghua University (www. tsinghua.edu) have teamed up to develop a technology to prolong the lifetime of OLED pan-

The technology provides an OLED lifetime of 100,000 hours.

els. According to *China Daily*, the company has developed a structure that delivers emission through a composite light-emitting layer that provides a 20-fold increase in the operational life of OLEDs. Visionox claims that current commercially produced high-definition screens have a 450- to 1000-cdm luminance, whereas the new technology can provide a lifetime of as much as 100,000 hours at a brightness of 1000 cdm.

—by Margery Conner >Visionox,

www.visionox.com.

## **Rarely Asked Questions**

Strange stories from the call logs of Analog Devices

#### **Op Amp Dedicated Feedback Pin Helps Achieve New Levels of Performance.**

or

This feedback pin is dedicated to all those op amps out there tonight!

**Q:** I've noticed a new pinout on some of your high-speed op amps. Why the change after all these years?

A: You're right. A few years ago, Analog Devices introduced a new pinout on some of our high-speed, high-performance amplifiers. This new pinout features a "dedicated feedback" pin, as Elvis is pointing out. Although the traditional SOIC pinout, which has been around for many years, performed admirably in the past, it imposes limitations as speeds continue to increase.

In a traditional SOIC pinout, pin 2 is the inverting input, pin 3 is the noninverting input, pin 4 is the negative supply, pin 6 is the output, pin 7 is the positive supply, and pins 1, 5, and 8 are typically no connects. But therein lies a problem: mutual inductance between pins 3 and 4 degrades the amplifier's second-harmonic distortion. To remedy this we rotated the pinout counter-clockwise by one pin on our LFCSP packages, breaking the coupling between the noninverting input and the negative supply. This change can improve second-harmonic distortion by up to 14 dB—a 500% improvement!

On some of our SOICs, we also provide a dedicated feedback pin, on pin 1. While this does not improve second-harmonic distortion, it greatly simplifies the circuit layout and reduces parasitic effects that can be detrimental to high-speed applications. In high-speed circuits, layout plays a large role in circuit performance. With

a traditional op amp pinout, getting the feedback signal to the inverting input requires it to be routed around or under the amplifier, with both options adding parasitics. With the dedicated feedback pinout, the feedback pin is right beside the inverting input, so all that is required to make the connection between the two pins is a resistor or a trace. The dedicated feedback pinout enables a very compact layout that requires less board area. It also reduces parasitics, which improves high-speed performance, and provides a more streamlined layout, which improves signal routing.

It's clear that a small, but innovative change like Analog Devices' dedicated feedback pin can make a big difference in the performance of your next high-speed amplifier design.

> To Learn More About High-Speed Amplifiers http://dn.hotims.com/34920-101

Contributing Writer John Ardizzoni is a Senior Application Engineer at Analog Devices in the High Speed Linear group. John joined Analog Devices in 2002, he received his BSEE from Merrimack College in N. Andover, MA and has over 30 years experience in the electronics industry.

Have a question involving a perplexing or unusual analog problem? Submit your question to: www.analog.com/ askjohn

For Analog Devices' Technical Support, Call 800-AnalogD

SPONSORED BY

## pulse

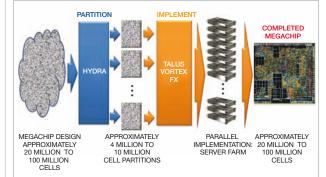

## EDA tool accelerates place and route for SOCs

Automation claims that its new Talus Vortex FX IC-implementation tool is the first to employ distributed computing for acceleration of placement and routing in SOCs (systems on chips). The company has also announced Talus 1.2, which integrates routing, timing analysis, and parasitic extraction to triple flat-block capacity to 3 million gates from the 1 million-gate capacity of Talus 1.1.

According to Bob Smith, vice president of product marketing at Magma, Talus Vortex FX's Distributed Smart Sync technology provides a threefold performance boost onto the improvements in standalone multithreaded capability of Talus 1.2 on a single server. On its own, the new Talus 1.2 system enables engineers to implement 1 million cells per day and perform crosstalk avoidance to detect and correct crosstalk violations during and MMMC (multimode/multicorner) analysis to manage multiple timing scenarios.

Talus 1.2 is currently in use for 28-nm designs at five large semiconductor companies, according to Smith, and the company has siliconproved the product in tape-

The Talus Vortex FX IC-implementation tool employs distributed computing for acceleration of placement and routing in SOCs.

optimization and implementation, advanced on-chip variation to ensure tight timing correlation throughout the flow, outs at the 40-nm node.

The Talus MX timing-andextraction engines borrow technology from Magma's Tekton timing analyzer and QCP sign-off extractor. It also features the Talus MX Router with enhanced global, tracking, and detailed routing capabilities.

The Magma Hydra designpartitioning and floorplanning tool provides the design input to Talus Vortex FX, which Magma licenses separately, to manage the distribution of parallel Talus place-and-route jobs across typically as many as 10 to 12 servers. To leverage the advantages of distributed computing, you must ensure that each server has an individual license available for the Talus 1.2 product. A typical hardware configuration uses servers with four to eight processor cores and 64 Gbytes of memory. During execution, Vortex FX synchronizes and aggregates the results of each Talus process to assemble the complete

SOC. – by Mike Demler ▷ Magma Design Automation, www.magma-da.com.

#### 400-Gbyte MLC solid-state drives target enterprises

Samsung Electronics Co Ltd is offering 100-, 200-, and 400-Gbyte MLC (multilevel-cell) solid-state drives for sampling. The drives target use as primary storage in enterprise systems. The devices use 30-nm-class MLC NAND-flash chips with a toggle DDR interface and a controller that uses a 3-Gbps SATA (serial-advancedtechnology-attachment) interface. Samsung claims that the drives can process random read commands at 43,000 IOPS (inputs/outputs per second) and random writes at 11,000 IOPS. The company compares that performance to a 15,000-rpm hard-disk drive, which has an IOPS rate of 350, amounting to a 120-fold gain in random-IOPS-write performance.

The solid-state drives have a 150-times-higher IOPS/ watt rate compared with 15,000-rpm hard-disk drives, making them able to process 150 times more data at the same power consumption, the company claims. The drives also feature an end-to-end data-protection function with an advanced data-encryption algorithm for drive reliability and security.

The solid-state-drive market is increasing at a solid pace, according to market-research-company projections. Gartner Inc (www.gartner.com) estimates that shipments of solid-state drives for servers and enterprise-storage systems will increase to 6.3 million units in 2014 from 324,000 units in 2009. Revenue for the solid-state-drive enterprise market should grow more than seven times from \$485 million to \$3.6 billion during the same period.

"As more and more server makers are adopting solidstate drives for use in eco-friendly platforms that consume less electrical power, the need for high-density drives in the server market is growing rapidly," says Byungse So, senior vice president for the memoryproduct planning and application-engineering team at Samsung Electronics. "We are now expanding our lineup to include high-density solid-state drives using MLC NAND-flash memory."

With the new drives, Samsung widens its range of densities to include 2.5-in., 50-, 60-, 100-, and 120-Gbyte drives using SLC NAND-flash memory and 2.5-in., 100-, 200-, and 400-Gbyte drives using MLC NAND-flash memory. The company also has 3.5-in., 100- and 200-Gbyte SLC drives. Samsung will begin mass-producing the MLC-based enterprise drives this month.—by Suzanne Deffree

Samsung Electronics, www.samsung.com.

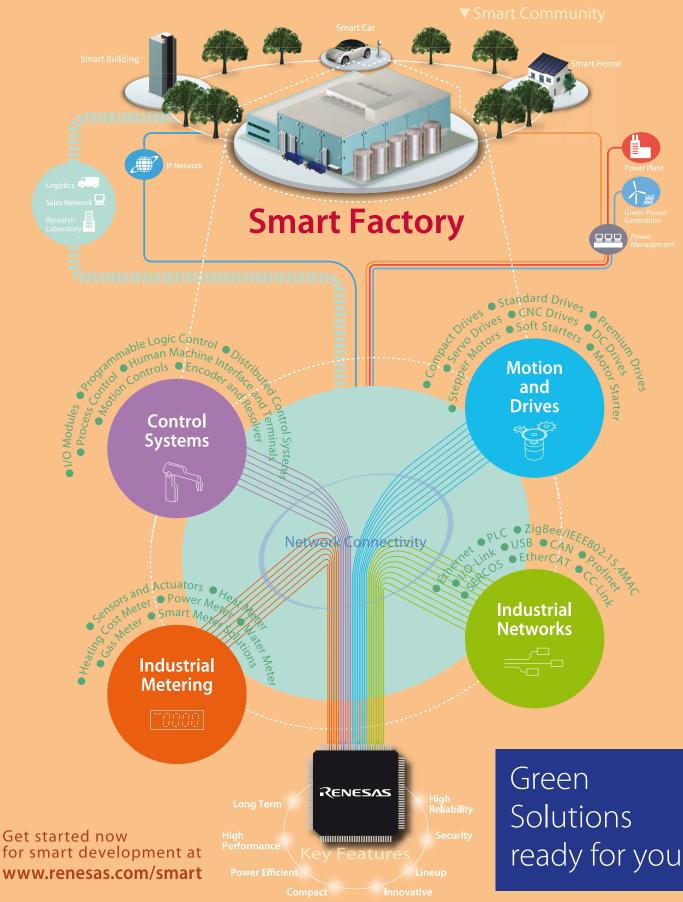

Renesas Electronics Corporation

#### RENESAS

## pulse

## Microcontrollers operate as fast as 120 MHz

Since the Cortex-M3 F-2 series of microcontrollers, which add more than 30 pin- and softwarecompatible parts to the STM32 family.

The company has also revealed its plans for the ARM Cortex-M4 and -M0 and plans to make products available for sampling starting in midyear and for production by the end of this year.

The company manufactures the STM32 F-2 in a 90-nm CMOS process, and it operates at clock speeds as high as 120 MHz. The devices include on-chip voltage regulators to convert external supplies of 1.65 to 3.6V for internal 1.2V core operation. The product portfolio offers a range of 64to 176-pin packages, including LQFP64, LQFP100, LQFP144, and UFGBA176, along with the WLCSP64, which measures less than 4×4 mm.

The STM205 includes one USB (Universal Serial Bus) port and 128 kbytes to 1 Mbyte of

flash memory, and the STM207 adds a second USB port and an Ethernet port. It also includes an 8- to 14-bit parallel camera interface that supas many as 64 branches in a cache memory. The 128-bitwide flash-memory interface enables simultaneous fetching of multiple 8-bit instructions and provides a 128-bit-wide prefetch queue for data.

The memory resources include 4 kbytes of battery-

The adaptive-real-time memory accelerator reduces programbranch-execution delay by saving as many as 64 branches in a cache memory.

ports data rates as high as 48 Mbytes/sec. The STM215 and STM217 include 512 kbytes of flash memory and add a cryptography/hash processor to implement 3DES (Triple Data Encryption Standard), AES (Advanced Encryption Standard) 256, and SHA (secure hash algorithm) 1 encryption. Three 2M-sample/sec ADCs are available, with an on-chip temperature sensor and a twochannel, 12-bit DAC.

The company's ART (adaptive-real-time) memory accelerator reduces program-branchexecution delay by saving

The Cortex-M3 F-2 series of microcontrollers adds more than 30 pin- and software-compatible parts to the STM32 family.

backed SRAM and 528 bytes of OTP (one-time-programmable) memory for storage of criti-

cal user data, such as Ethernet

MAC (media-access-control) addresses or cryptographic keys.

An evaluation board, the STM3220G-Eval, is available as a vendor-neutral platform and comes with no IDE (integrated device electronics) or JTAG (Joint Test Action Group) cable, supporting a choice of development environments.

The STM Cortex-M3 F-2 series is now available for sampling for OEMs and will be available for production during the first quarter of this year. Prices for the F-2 series start at \$3.18 (10,000) for the ST-205 with 128 kbytes of flash memory.

—by Mike Demler

STMicroelectronics, www.st.com/stm32.

#### GARTNER PREDICTS INDIAN PC SHIPMENTS TO GROW 25% IN 2011

PC demand is growing beyond the largest cities in India and will see shipments rise nearly 25%, according to a recent forecast from Gartner Inc. The market-research company has estimated that Indian PC shipments will total 13.2 million units in 2011, a 24.7% increase from 2010 levels. "There is an increased aspiration to own a PC in India," says Vishal Tripathi, principal research analyst at Gartner. "The younger generation is contributing to the large-scale adoption of PCs in India in a significant way. Besides reading and surfing the Internet, the usage of PCs for watching movies, listening to music, and gaming is playing a pivotal role in driving demand."

Gartner notes that vendors are seeing an increasing demand from smaller cities in India in which PC penetration has grown considerably. The company attributes that growth to rising income and declining PC prices.

The research company predicts that mobile PCs will outnumber desktops in India by the fourth quarter of this year. Still, the total number of desktop shipments should be higher than those of mobile PCs. In 2011, the desktop-PC market will grow 5%, totaling 7.2 million units, and mobile-PC shipments will grow 61% with 5.9 million units. "The Indian PC market is far from reaching maturity, unlike the other developed countries," says Tripathi. "India contributes significantly to the overall growth of PC shipments worldwide."—by Suzanne Deffree Gartner, www.gartner.com.

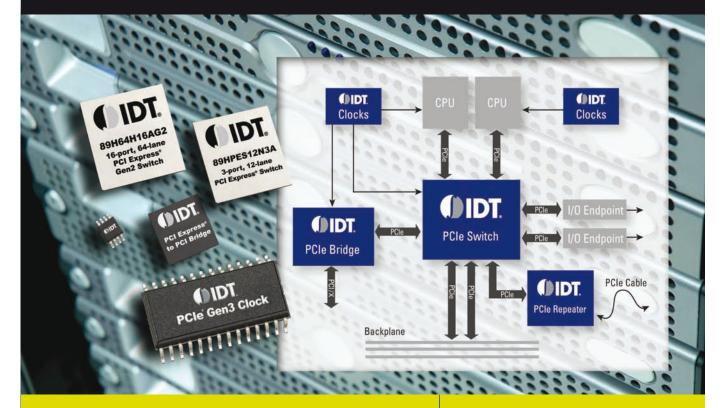

### Integrated Device Technology – Leader in PCI Express<sup>®</sup> Solutions

#### **PCI Express Switches**

Industry's most comprehensive family of high-performance, scalable PCIe switching solutions

- Gen 1 and Gen 2 Portfolio

- Up to 64 lane and 24 port devices

- Highly flexible port configurations

- Unprecedented 8 non-transparent bridging (NTB) functions to enable multi-root applications

#### **PCI Express Repeaters**

5Gbps Gen 2 PCIe Signal Repeaters

- Four and eight channel signal repeaters

Compensates for cable and PCB trace attenuation and ISI jitter

- Programmable receiver equalization to 30dB and de-emphasis to -8.5dB

- Leading edge power minimization in active and shutdown modes

- No external bias resistors or reference clocks required

- Channel mux mode, demux mode, 1 to 2 channels multicast, and Z-switch function mode

#### **PCI Express Bridges**

High performance PCIe bridging to legacy PCI and PCI-X protocols

- Ultra low power version for consumer applications

- Forward mode buffer optimization

- Only PCI Express bridges with Short Term Caching for significant improvement in PCI Read performance

- Pin compatibility with competitive offering for dual sourcing solution

#### **PCI Express Clocking Solutions**

Industry's broadest offering of PCIe Gen1, Gen2 and Gen3 clock generation and buffering solutions

- World's First PCI Express Gen3 Family of Timing Devices

- Clock Generators and Synthesizers

- Spread Spectrum Clock Generators

- Fanout Buffers and Muxes

- Jitter Attenuators

- Frequency Translators

- Zero Delay Buffers

## **Integrated Device Technology**

The Analog and Digital Company<sup>™</sup>

For more information visit us online at www.IDT.com

## pulse

## VOICES

#### Samsung Electro-Mechanics' Jong-Woo Park: targeting smart-grid, electric-vehicle, and biotechnology applications

Samsung Electro-Mechanics has grown continuously through constant investment and R&D since its establishment in 1973 to become one of the leading electronics-parts manufacturers, according to Chief Executive Officer Jong-Woo Park. He says that the company has continued to break quarterly sales records since last year, becoming the fifth-largest electronics-parts maker. Sales reached approximately 5.5 trillion Korean won on a consolidated basis in 2009 and approximately 3.5 trillion Korean won in the first half of 2010. *EDN* recently conducted an e-mail interview with Park, a portion of which follows. For the complete version, go to www.edn.com/110120pa.

#### What product lines does Samsung Electro-Mechanics offer?

Samsung now pro-A duces essential parts and components for mobile phones, TVs, computers, and other advanced IT products. For mobile phones, Samsung makes mobile-phone substrates, camera modules, precision motors, and MLCCs [multilayer ceramic capacitors]. In addition, Samsung makes components for display devices, including power modules, network modules, digital tuners, and MLCCs, and the company makes components for computers, including network modules, semiconductor substrates, and MLCCs.

#### What is the significance of the MLCCs?

MLCCs and PCBs [printed-circuit boards] have greatly contributed to corporate growth in recent years. MLCCs are essential parts for all kinds of electronic products, including mobile phones, PCs, and TV sets. The device controls the flow of current in electric circuits.

#### How have PCBs helped Samsung's business?

In the PCB-forsemiconductor seqment, we have maintained the top share of the world market since 2007. This [achievement] has been made possible by our launching new models, such as one with the world's thinnest substrate, at the right time and securing stable product yields. The semiconductor substrate is an auxiliary part that acts as a bridge between the semiconductor and the motherboard. Semiconductors, which have high density, cannot be directly attached to the main PCB in the way that condensers, resistors, and other passive parts can. Thus, semi-

conductor substrates are essential for transferring semiconductor signals to the motherboard.

#### Could you comment on your supply-chain-management capabilities?

Since I was appointed chief executive officer in January 2009, we have built a companywide SCM [supplychain-management] system to prevent inefficiency and realize smart management. SCM is a companywide innovation program designed to ensure operational predictability by seamlessly connecting all parts, from customers to suppliers. The SCM solution guarantees just-in-time production and reduces resource waste, raising profitability.

Of course, even though we build an SCM system, it is of no use if we do not use it properly. Top management must be the first to understand the system and apply it in everyday operations. Then, the rest of the work force must all follow the rules and processes that have been laid out to achieve the expected results. This [approach] will also allow us to work smarter.

#### What are your plans for the future?

We will join the ranks of the top-tier players by 2015 by improving the way individual employees do their jobs and realizing even greater changes within the company. Samsung is now expanding the weight of value-added products in the current IT-based product portfolio. At the same time, internal competitiveness is being strengthened and new technology developed to advance into new business areas.

To this end, we plan to grow as a top-tier maker of MLCCs, substrates, and power supplies—all core business areas. At the same time, we will take advantage of our core technologies in materials, optics, and radiofrequency devices to cultivate new growth opportunities in the smart grid, EV (electricvehicle) power-supply, EV traction-motor, biotechnology, and health-care fields.

#### Can you elaborate on those applications?

In the smart-grid sector, Samsung is now involved in power conversion-photovoltaic inverters and smart meters for remote measuring-and module services. The company is also participating in various testbed projects organized by the Korean government. We also plan to expand into drive motors, electric-power-control systems, quick chargers, and parts for automotive electrical systems by leveraging our technologies related to power supplies and motors.

As for biotechnology, we are now promoting cell chips for toxicity monitoring and drug-releasing systems by applying MEMS [microelectromechanical-system] technology obtained through our ink-jet-printer business. The future strategy of Samsung is to expand into energy, environment protection, EV parts, and biotechnology by taking advantage of convergence and modularization.

-interview conducted and edited by Rick Nelson

## The World's Standard.

Basic Visualization - 40 to 500 MHz

### Oscilloscopes from Basic to Bench and Beyond.

Whatever your need, there is a Tektronix oscilloscope to fill it. Tektronix offers the world's broadest portfolio of oscilloscopes to debug and test tomorrow's designs, today. Start with Tektronix Basic oscilloscopes: fast, familiar and affordable; they're what you know and trust. Our Bench oscilloscopes provide next-level productivity, with the feature-rich tools you need to debug today's complex mixed signal designs. And for those who demand fast, flexible, in-depth PHY layer analysis, our Performance oscilloscopes offer the industry's best signal fidelity, verification and characterization capabilities to help you shorten your design cycles.

No wonder 8 of 10 engineers worldwide trust Tektronix to help them bring advanced designs to market on time and on budget. Wherever you're going, we'll get you there.

See why Tektronix is the World's Standard in Oscilloscopes and download your free Oscilloscope Primer.

www.tektronix.com/worldstandard

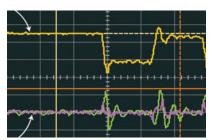

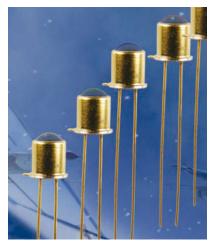

#### Remote photo sensing

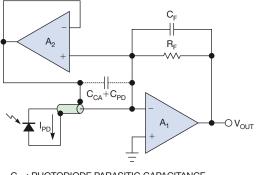

hotodiodes transform a basic physical occurrence, light, into an electrical form, current. Design engineers methodically convert the photodetector's current to a usable voltage, which makes the manipulation of the photodiode signal manageable. There are many ways to approach the photosensing-circuit problem, but one issue came to mind as I read the comments in the Talkback section for a recent column (**Reference 1**). A reader requested a circuit that reduces the noise impact of a photodiode with a large parasitic capacitance.

A classic photo-sensing system circuit has a photodiode, an operational amplifier, and a feedback resistor/capacitor pair at the front end. Recalling a circuit from another column, in this circuit, the photodiode, amplifier, and feedback-capacitance elements limit the bandwidth of the circuit (**Reference 2**). Yet another column details the stability of this circuit (**Reference 3**).

When sensing with a photodiode with a large parasitic capacitance or from a remote site, the input of the amplifier has a large capacitance across its input. The result of this added capaci-

$\rm C_{PD}$ : PHOTODIODE PARASITIC CAPACITANCE  $\rm C_{CA}$ : CABLE CAPACITANCE

Figure 1 You can use bootstrapping to eliminate diode capacitance and cable capacitance from the transimpedance-design problem.

tance increases the circuit's noise gain unless you increase the amplifier's feedback capacitor. If the feedback capacitor,  $C_{\rm F}$ , increases, the bandwidth of the circuit decreases.

To fix this problem, you can use a bootstrap circuit (Figure 1). Photodiodes with a relatively low diode capacitance do not benefit from this circuit. A unity-gain buffer,  $A_2$ , removes the cable's capacitance and the photodiode's parasitic capacitance from the input of the transimpedance amplifier,  $A_1$ .

When designing this circuit, you'll find that the type of amplifier you se-

lect for  $A_2$  is somewhat easy. The only important performance specifications are low input capacitance, low noise, a wider bandwidth than  $A_1$ , and low output impedance.

In this design,  $A_2$ 's input capacitance is the only capacitance that plays a role in the ac-transfer function of the transimpedance system. The input capacitance of the buffer replaces the summation of the input capacitance of  $A_1$ , the cable capacitance, and the parasitic capacitance of the photodiode. A good rule of thumb is to have  $C_{A2} << (C_{A1} + C_{CA} + C_{PD})$ , where  $C_{A1}$  and  $C_{A2}$  represent the sum of their input differential and common-mode capacitance.

With this design, you exchange one noise problem,  $A_1$ , with another,  $A_2$ . The unity-gain buffer removes the noise effect from  $A_1$ . A good approach is to make the noise of  $A_2$  less than or equal to that of  $A_1$ .

The difference between the input signal and the output signal in this system falls across the cable/diode capacitance. You can keep this difference low

#### A<sub>2</sub>'s input capacitance is the only capacitance that plays a role in the ac-transfer function.

by selecting  $A_2$  with wider bandwidth than  $A_1$  and keeping  $A_2$ 's output impedance low.  $A_2$ 's gain roll-off introduces an upper limit for the bandwidth improvement, making  $A_2$ 's bandwidth much greater than that of  $A_1$ . This circuit requires stability optimization as you balance  $C_F$  and the input capacitance of  $A_2$  (references 4 and 5).EDN

#### REFERENCES

Baker, Bonnie, "A good holiday-season project," *EDN*, Dec 15, 2010, pg 18, http://bit.ly/fG59Ly.

Baker, Bonnie, "The eyes of the electronic world are watching," *EDN*, Aug 7, 2008, pg 24, http://bit.ly/i5lr65.

Baker, Bonnie, "Transimpedanceamplifier stability is key in light-sensing applications," *EDN*, Sept 4, 2008, pg 24, http://bit.ly/hG4bNW.

Graeme, Jerald G, Photodiode Amplifiers: Op Amp Solutions, McGraw-Hill, 1996, ISBN 0-07-024247-X.

Kurz, Dov, and Avner Cohen, "Bootstrapping reduces amplifier input capacitance," *EDN*, March 20, 1978.

Bonnie Baker is a senior applications engineer at Texas Instruments. You can reach her at bonnie@ti.com.

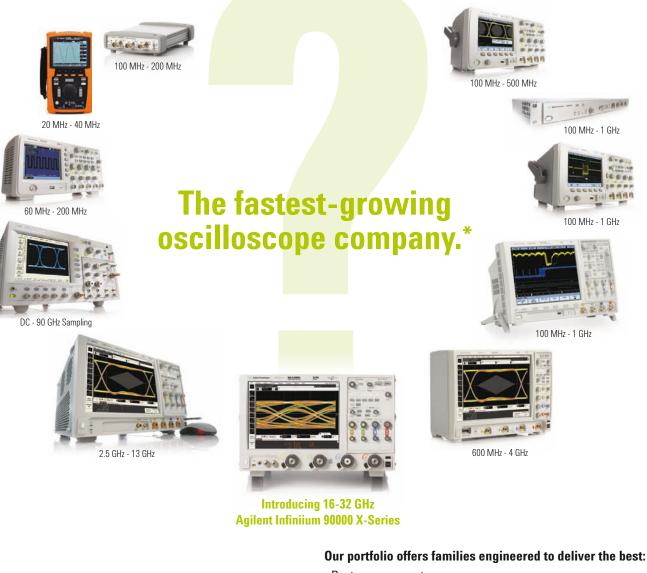

### Who makes the fastest real-time oscilloscopes?

- · Best measurement accuracy

- · Broadest measurement capability

- Best signal visibility

- · More scope than you thought you could afford

Are you using the best scope? Take the 5-minute scope challenge and find out. www.agilent.com/find/scopecheck

u.s. 1-800-829-4444 canada 1-877-894-4414

#### **PRY FURTHER AT EDN.COM**

+ Go to www.edn.com/pryingeyes for past Prying Eyes write-ups.

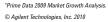

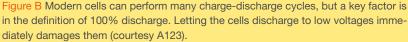

#### The Schauer TB10012 battery charger

his charger worked fine for 30 years. When it stopped working a couple of years ago, I pried into its interior to see what was wrong. It turns out that the failure was purely mechanical. I must have dropped the unit, which dislodged the copper PCB (printedcircuit board) from its isolated mounting and allowed it to short-circuit the case. In addition, the movement of the heat sink caused a pin to break off the output transistor that was mounted on it. I repaired the unit by pushing the heat sink back onto the insulated boss and re-soldering the wire to what remained of the transistor pin. It seemed that the charger was still broken until I remembered that it was designed to have no output until it was hooked to a battery. Once I biased up the control board with a few volts from a dead motorcycle battery, the charger worked fine, including the adjustable output voltage on the control board. An important factor in the longevity of the unit is that the designers did not use electrolytic capacitors.

The design uses puckstyle diodes similar to those in automotive alternators. Manufacturers solder them directly to the copper heat sink. The two wires to the diodes are the ends of a centertapped transformer's secondary winding. A thermal circuit breaker limits output current in case the output transistor short-circuits. The breaker is wired into the negative side of the output. The mounting of the control PCB allows an adjustment potentiometer to extend from the back of the case. The board regulates the output voltage and prevents output unless an attached battery is present. The charger's main transformer features primary and secondary windings on separate bobbins, similar to the high-isolation transformers that medical equipment uses. The case includes a ground wire in accordance with UL (Underwriter Laboratories) requirements.

The output pass transistor has two thick wires soldered to each of its pins. The wire from the control PCB caused stress, which broke off the transistor's base pin.

A thin copper sheet serves as a heat sink. A square hole in the bottom snaps over a plastic mounting boss in the outer case. The heat sink operates at 15V, the raw unregulated rectified output of the transformer.

## Support Across The Board. From Design to Delivery<sup>™</sup>

Faster and easier than ever before. Our commitment to customer service is backed by an extensive product offering combined with our supply chain and design chain services - which can swiftly be tailored to meet your exact needs. We have dedicated employees who have the experience to provide the highest level of customer service with accuracy and efficiency. All of our technical experts are factory certified on the latest technologies, providing you the expertise to move projects forward with speed and confidence.

Avnet offers the best of both worlds: extensive product and supply chain knowledge, and specialized technical skill which translates into faster time to market - and the peace of mind that comes from working with the industry's best. Avnet is ranked Best-In-Class\* for well-informed sales reps, knowledgeable application engineers and our design engineering services - proof that we consistently deliver:

> Industry recognized product expertise

> Specialized technical skills

Ready. Set. Go to Market.<sup>™</sup> Visit the Avnet Design Resource Center<sup>™</sup> at: www.em.avnet.com/drc

Accelerating Your Success<sup>™</sup>

1 800 332 8638 www.em.avnet.com

Follow us on Twitter! www.twitter.com/avnetdesignw

#### NECHATRONICS INDESIGN FRESH IDEAS ON INTEGRATING MECHANICAL SYSTEMS, ELECTRONICS, CONTROL SYSTEMS, AND SOFTWARE IN DESIGN

## You can't just say it's reliable

Understanding the physics of failure and having a systems approach are essential to modern engineering.

**GA** man's got to know his limitations." This line is one of the more memorable that Clint Eastwood delivers in the movie *Magnum Force*, and it shows great wisdom. How does this line relate to engineering-system reliability, however?

What do we mean when we say that someone is reliable? Is it possible to say that a person is always reliable or just sometimes reliable, in all circumstances or in just some circumstances? You must apply the same questions to an engineering-system design because reliability cannot be an afterthought.

As you become more dependent on complex mechatronic systems, it is not sufficient to understand just how they work; you must also understand how they fail. Fault-tolerant system design, not just fault-tolerant component or subsys-

#### As mechatronic systems become more complex, the interactions among the subsystems become more difficult to manage, and this integration affects the overall system reliability.

tem design, has become paramount. Reliability is the probability that an item performs a required function under stated conditions for a stated period of time. An engineer thus must define the functions a system must perform, the boundary conditions under which the system will operate, and the time during which the system must be reliable.

Tim Kerrigan, a fluid-power consulting engineer at Milwaukee School of Engineering's Fluid Power Institute, works to ensure that industrial and government systems are reliable. He believes that a physics-of-failure approach to reliability is consistent with the model-based approach of modern mechatronic-system design. It uses modeling and analysis to design reliability into a system, perform reliability assessments, and focus reliability tests in areas in which they will be most effective. The approach involves understanding and modeling the potential failure mechanisms, including fatigue, wear, and temperature; the failure sites; and the failure modes.

The failure modes of a mechatronic system include those of mechanical, electrical, computer, and control subsystems—that is, hardware and software failures. A physics-of-failure approach can improve reliability, reduce the time to deploy systems, reduce testing and costs, and increase customer satisfaction.

As mechatronic systems become more complex, the interactions among the subsystems—mechanical, electrical, computer, and control—become more difficult to manage, and this integration affects the overall system reliability. Therefore, an assessment of overall system

Kevin C Craig, PhD, is the Robert C Greenheck chair in engineering design and a professor of mechanical engineering, College of Engineering, Marquette University. For more mechatronics news, visit mechatronics zone.com.

reliability must have an adequate margin for safety. A useful analogy in this case is a feedback-control system. It provides great benefits, but a feedback-control system can become unstable if there is an imbalance between the strength of corrective action, or gain, and system dynamic, or phase, lags. You quantify model uncertainty by assuming that either gain changes or phase changes occur and that the tolerances of gain or phase uncertainty are the stability margins, gain margin, and phase margin. Real systems must have adequate stability margins. Real systems must also have adequate reliability margins.

Mechatronics can enhance the reliability and fault tolerance of a system with prognostics, diagnostics, and builtin test capabilities. The additional sensors and control elements must be reliable, and they add cost. The long-term cost of unreliability is much larger, however, than the initial design cost of reliability. In addition, designing for reliability enhances energy efficiency and sustainability. Reliability and fault tolerance are competitive advantages in the commercial market and absolute requirements in the healthcare, military, and transportation sectors.EDN

## Introducing EDN's New Microsite on LEDs

## Your complete source for up-to-the-minute information on LEDs and their applications.

Latest News from the Editors at EDN, Design News and other Engineering Magazines

Blogs, including Margery Conner's Popular "Power-Source" Blog

Resource Center, Including White Papers, eBooks, Tutorials, Webcasts and More

Videos, Including

Design Tips, Application

Demos, and More

Updates on Future In-Person Workshops and Seminars, like this one!

Fun Challenges to Test Your

Knowledge of LEDs

#### Check It Out Today at www.edn.com/leds

OFFLOADING QUEUE AND TRAFFIC MANAGEMENT TO HARDWARE REDUCES DESIGN COMPLEXITY, IMPROVES **APPLICATION EFFICIENCY, AND** MAXIMIZES PERFORMANCE.

Available Bandwidth

Next Right

## HARDWARE-BASED VIRTUALIZATION **EASES DESIGN WI MULTICORE PROCESSORS**

BY SATISH SATHE • APPLIEDMICRO

oday's SOC (system-on-chip) processors integrate a diversity of cores, accelerators, and other processing elements. These heterogeneous multicore architectures provide increased computational capacity, but the resulting complexity also poses new challenges for embedded-system developers across a variety of applications, including control-plane processors, video servers, wireless base stations, and broadband gateways. Discrete cores each have full access and control of their resources. Such predictable access allows straightforward management and deterministic performance in applications with real-time constraints. In a multicore architecture, however, cores share access to resources, and potential contention complicates many design factors, such as processing latency and deterministically handling interrupts. To provide deterministic behavior equivalent to that of single-core devices, multicore architectures have begun to implement resource-sharing and management techniques that have been proved in network communications. These architectures use established queue- and traffic-management techniques to efficiently allocate resources among multiple cores, maximize throughput, minimize response latency, and avoid unnecessary congestion.

#### **RESOURCE VIRTUALIZATION**

From an architectural standpoint, SOCs are complex systems with multiple cores that connect across a highspeed fabric to a variety of controllers and resources (Figure 1). In many ways, the myriad interactions within an SOC resemble a communications network with multiple sources, or cores, that interconnect to the same destinations, including memory, peripherals, and buses. Not surprisingly, bandwidth-management techniques, such as virtualization, which designers developed to improve network efficiency, have proved useful in managing traffic among multiple processor cores and shared peripherals.

Virtualization of on-chip resources enables cores to share access; this shared access is transparent to applications. Each application can treat a resource as if it were the sole owner, and a virtualization manager aggregates shared ownership—measured by the amount of allocated bandwidth. Virtualizing and sharing access to resources require both a queue manager and a traffic manager. Applications use one or more queues to buffer access to a resource. Virtualization adds events or transactions to the queue and pulls them off when the re-

#### AT A GLANCE

The complexity of multicore processors poses new challenges, such as the risk of contention for access to shared hardware resources, for embedded-system developers.

To manage the myriad interactions within a multicore SOC (system on chip), you must apply queue- and traffic-management techniques that have been proved in network communications.

Virtualization of on-chip resources es enables each application to treat a resource as if it were the sole owner.

Hardware-based virtualization accelerates the software virtualization layer, enabling faster development with simplified debugging and increased system reliability.

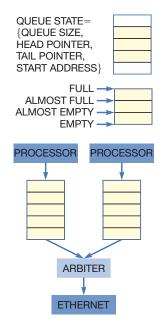

source is available. Queues comprise a list of buffer descriptors pointing to data in a buffer, and you can implement queues in many ways, depending on the needs of the applications. The number of supported queues varies in an SOC from a few hundred to hundreds of thousands to meet the needs of various applications.

The queue manager updates the queue state—that is, the queue size, head pointer, tail pointer, and start address and maintains fill levels and thresholds, including full, almost full, almost empty, and empty. The queue manager also provides full memory management for each queue, including allocation and deallocation of buffers from free pools and checking of access rights when an event is added to a queue (**Figure 2**). Multiple requesters may simultaneously add descriptors to one or more queues, as well as allow selection from multiple queues waiting for a service.

The manager serves as the arbitrator for available bandwidth among queues assigned to the same resource. It performs this task not only between applications sharing a resource but also among the multiple queues an application may have to enable QOS (quality of service).

Traffic management employs policing and shaping mechanisms to measure and control the amount of bandwidth assigned to a flow or a group of flows. Policing controls the rate at which the traffic manager adds events to a queue, and shaping is the rate at which the traffic manager removes events from the queue. For the most control and ability to manage queue priority, you must implement policing and shaping on a per-queue basis. The traffic manager also maps multiple queues to a single shared resource based on a predefined servicing algorithm.

By bringing queue and traffic management together, you can provide reliable, end-to-end QOS. This approach allows multiple paths to share a resource without negatively affecting bandwidth subscriptions. Fine-grained QOS supports SLAs (service-level agreements), guaranteeing minimum, average, and maximum bandwidth on a per-flow basis. Developers can implement queue levels for marking and metering traffic to prevent congestion. Early notification of congestion allows the queue manager to take corrective action through feedback to traffic sources to eliminate the unnecessary processing of packets that are

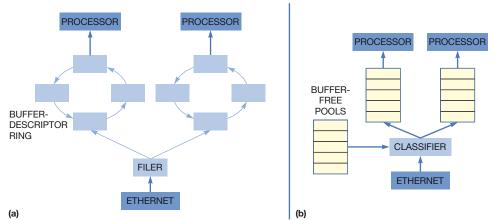

Figure 1 Next-generation SOCs are complex systems with multiple cores accessing the same shared resources. These systems resemble a network fabric and can benefit from the same queue- and traffic-management technology that communications networks use.

Figure 2 Hardware-based virtualization offloads queue management from application processors, including updating queue states, maintaining fill levels and thresholds, allocating and deallocating buffers, and confirming access rights when an application accesses a queue.

likely to be dropped or, ideally, to avoid congestion altogether.

For example, a queue- and trafficmanagement-based Ethernet driver prevents any one processor from unfairly monopolizing port bandwidth. It also guarantees bandwidth allocations and maximum-latency constraints regardless of other queue states. The driver supports a choice of arbitration schemes-strict priority or weighted round robin, for example-and facilitates reliable real-time services, such as video streaming. In the end, multiple sources can share the Ethernet port without adversely affecting bandwidth subscriptions. Tasks such as IP (Internet Protocol) forwarding become straightforward to implement robustly, and latencysensitive applications, such as audio or video delivery, benefit from deterministic and reliable port management. In addition, when you implement the queue and traffic management in hardware, the driver can maintain end-to-end QOS with little to no software overhead.

#### THE VIRTUALIZATION LAYER

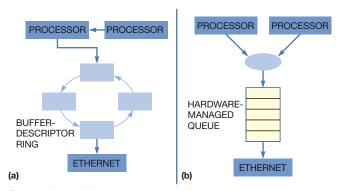

Early multicore SOCs, like the original network processors, left all of the work of virtualizing resources to developers. Applications, to some degree, had to recognize that they might share a resource with other applications. When an application used a shared resource, it had to do so in a way that allowed coexistence with other applications. The operating system also needed to support virtualization.

In a traditional architecture, processors manage their own access to shared resources through a software layer (Figure 3a). Processors must be aware of what resources are available and how often they can use them. As the number of processors increases, so does the complexity of resource sharing. One downside of software-based virtualization is that it introduces overhead to every transaction to store and later retrieve packets. Such overhead consumes processor cycles and introduces complexity to the coding process. It also places the burden of bandwidth management and meeting subscription guarantees on the virtualization software. Even when using tools to automate the creation of virtualization code, developers still must troubleshoot application interactions as they pass through the virtualization code.

The added overhead and complexity of virtualization have limited the use of multicore SOCs. Queue and traffic management, however, is a fairly deterministic process that you can implement in hardware. Developers configure queues once for an application, and the hardware mechanisms can then completely offload queue management, thus restoring substantial computational cycles

back to the application processors. The ability to dynamically change allocations allows modification of the overall configuration at runtime to accommodate changing task loads.

In an architecture using a hardwarebased queuing and synchronization mechanism, each processor operates independently of the others (**Figure 3b**). Through virtualization of resources, sharing becomes transparent to the applications. The mechanism allocates each processor and each task resource bandwidth, and each processor and task operates as if it were the only controller of the resource. Although the gains from implementing queue and traffic management vary from application to application, hardware-based resource virtualization and sharing significantly improve system efficiency.

A hardware-based virtualization layer removes or accelerates the softwarevirtualization layer. Offloading virtualization substantially increases processor efficiency. In some cases, hardwarebased virtualization removes the need for software-based virtualization, other than during initial configuration. In other cases, hardware-based queue and traffic management significantly accelerates virtualization software in the datapath.

A hardware-based virtualization layer also lowers design complexity and speeds development because it eliminates the need for developers to implement and design around the virtualization layer. This approach simplifies design and speeds time to market. This hardware-based layer also increases determinism. Elimination of virtualization overhead reduces a major source of system interrupts. This elimination in turn reduces processing latency and increases system responsiveness.

Another benefit of this approach is

Figure 3 In a traditional architecture, processors manage access to shared resources through a software layer (a). As the number of processors increases, so do the complexity and overhead of resource sharing. Hardware-based virtualization eliminates the need for a software-based virtualization layer (b). In addition to offloading queue and traffic management, resource sharing becomes transparent to applications, and each processor can operate independently of the others.

that it simplifies debugging. Because virtualization and resource sharing are hardware functions, the virtualization layer itself is not part of the development process. However, developers still have full access to and control of queues if necessary for troubleshooting. A hardwarebased virtualization layer also increases reliability because hardware-implemented queue and traffic management is not vulnerable to many of the issues that can arise with a software-based implementation. For example, if the core-handling software-based virtualization becomes compromised, the entire system is vulnerable. With a hardware-based implementation, there is no centralized control routine to compromise.

#### **PROCESSOR OFFLOADING**

The level of supported queue offloading depends on the implementation. For example, some SOCs might provide locking mechanisms but not perform all state management of queues. Ideally, developers want a flexible system that supports different configurations, is straightforward to integrate with software, and minimizes the software changes necessary to adopt the SOC. A virtualization mechanism may be efficient; if it requires significant deviation from traditional programming models, however, porting application code will increase system cost and delay time to market.

How you implement queues can also affect system performance. For example, queue location affects which processors can access those queues. Some queues must reside in memory types, be spread across multiple chips, or be tied to a resource. Dynamically allocated queues give developers the flexibility to appropriately partition queues to applications and resources. For systems using multiple multicore SOCs, the ability to manage queues over a system bus, such as PCIe (Peripheral Component Interconnect Express), enables sharing of resources not just between cores on the same SOC but also between those on different SOCs. For example, a cluster of processors can share a single forwarding database. Alternatively, a multiple-SOC system may have a single deep-packet-inspection engine that applications running on different SOCs must access. Such multichip sharing of resources allows even further virtualization of system resources.

Battery-Powered Wi-Fi® Modules for Sensing Applications NEW - Now Features 11 Mb/s & Enterprise Security Low-Cost Multi-Function FHSS Modules NEW - Now Features Tree-Routing with Redundancy Enhancement

Low-Cost Low-Power 802.15.4 Modules Available in 1 mW Low-Power and 100 mW Extended Range

**Optional Chip Antenna**

✓ Faster time-to-market

✓ Reduce design engineering costs

#### SFCC, CI, ETSI certified

#### Sield proven

Building on three decades of experience in the design and manufacture of low-power radio frequency (RF) products, today RFM is enabling OEM design engineers to wirelessly connect and network more devises, equipment, and processes than ever before. Visit www.RFM.com for more information about these and other wireless standards- and proprietary-based communications and networking products.

|                        | FREQ    |         | MAX DATA<br>RATE |          |         | MAX RANGE    |               |               |               |                 | RF POWER          |      |       |        |        | STANDARD |          |             | NETWORK |            |            | INTER-<br>FACE |           |              |

|------------------------|---------|---------|------------------|----------|---------|--------------|---------------|---------------|---------------|-----------------|-------------------|------|-------|--------|--------|----------|----------|-------------|---------|------------|------------|----------------|-----------|--------------|

|                        | 900 MHz | 2.4 GHz | 250 kb/s         | 500 kb/s | 11 Mb/s | Indoor 100 m | Indoor >100 m | Outdoor 100 m | Outdoor 250 m | Outdoor 1,000 m | Outdoor >10,000 m | 1 mW | 10 mW | 100 mW | 250 mW | 1W       | 802.15.4 | Proprietary | 802.11  | Mesh / S&F | Multipoint | Peer-to-peer   | UART Only | I/O and UART |

| DNT900*                | 1       |         |                  | 1        |         |              | 1             |               |               |                 | 1                 | 1    | 1     | 1      | 1      | 1        |          | 1           |         | 1          | 1          | 1              |           | 1            |

| DNT2400*               |         | 1       |                  | 1        |         |              | 1             |               |               |                 | 1                 | 1    | 1     | 1      |        |          |          | 1           |         | 1          | 1          | 1              |           | 1            |

| LPR2430*               |         | 1       | 1                |          |         | 1            |               | 1             |               |                 |                   | 1    |       |        |        |          | 1        |             |         |            | 1          | 1              |           | 1            |

| LPR2430ER <sup>+</sup> |         | 1       | 1                |          |         |              | 1             |               |               | 1               | 1                 | 1    | 1     | 1      |        |          | 1        |             |         |            | 1          | 1              |           | 1            |

| WSN802G*               |         | 1       | -                |          | 1       | 1            |               | 1             |               |                 |                   |      | 1     |        |        |          |          |             | 1       |            | 1          |                |           | 1            |

+LPR series also available with Chip Antenna.

One of the greatest design challenges in multichip architectures is partitioning tasks in a way that equally spreads resource requirements among all processors. In software-based virtualization, this process can be time-consuming and places a burden on designers, including the challenge of efficiently managing free memory pools. In addition, any change in software can result in a shift in resource requirements, requiring developers to repartition the system. Many of these issues apply to both asymmetrical and symmetrical multiprocessor architectures.